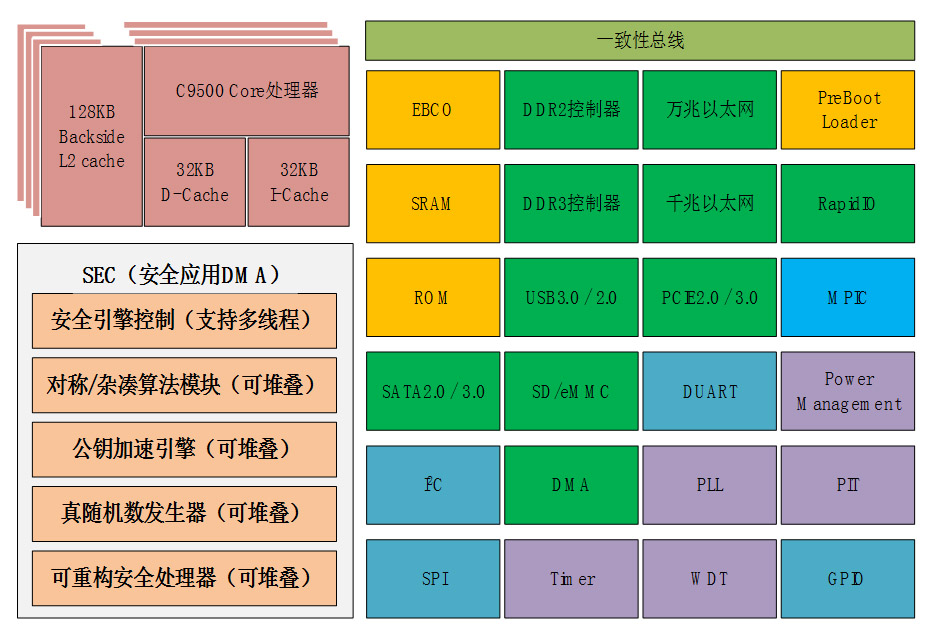

網絡通信及邊緣計算芯片設計平台CSOC9500,基于蘇州國(guó)芯自主知識産權的C*Core 32位高性能(néng)信息安全處理器C9500,支持ISA V2.05指令集架構(Power Instruction Set Architecture),兼容NXP E500MC核。該平台提供用于設計多核處理器,多種(zhǒng)高速接口,如萬兆以太網、PCIE 3.0、USB 3.0、DDR、RapidIO等,提供國(guó)密算法和國(guó)際主流密碼算法IP,集成(chéng)多種(zhǒng)抗攻擊防護方法,以及常用的通信接口IP。基于該平台設計的安全芯片主要用于工業控制安全,系統控制,可信計算等領域。

典型量産應用

H2040高性能(néng)嵌入式32位處理器采用C9500架構的四核PowerPC處理器,包含了網絡互聯、電信/數據通信和無線基礎設施應用所需要的高性能(néng)數據通路接口邏輯、網絡以及外設等總線接口。

H2040可用于路由器、交換機、基站控制器和通用嵌入式計算中的綜合控制、數據通路和應用層處理。與多台分立器件相比,它的高度集成(chéng)提供了顯著的性能(néng)優勢,同時也大大簡化了電路闆的設計。

芯片正常工作頻率在1200MHz,集成(chéng)GMAC,PCIE,DDR等高速接口。

H2040項目生産工藝采用TSMC28HPC+,工作溫度-40 ~125 ℃。

√ 每核獨立32-KB L1-cache,32-KB L2-cahce;

√ 每核獨占128kB二級緩存;

√ 支持3級指令:user、supervisor和hypervisor;

√ 獨立的boot和reset;

√ ROM/SRAM

√ PCIE3/USB3/USB2/

SATA2/SATA3/SRIO2/RapidIO

√ SD/eMMC

√ SPI/I2C/UART/MPIC

√ 4路JobRing進(jìn)行算法調度

√ 公鑰算法加速引擎

☆ Diffie Hellman/SM2/SM9/ECC/RSA

√ 對(duì)稱算法加速引擎

☆ SM1/SM4/SM6/SSF33/AES/DES/3DES

√ 哈希算法加速引擎

☆ SM3/MD5/HMAC/SHA0/SHA1/

SHA2(224/256/384/512)

√ RSCP可重構對(duì)稱算法加速處理器

√ TRNG真随機數發(fā)生器

√ CRC加速器

√ 防側信道(dào)攻擊

√ 可獨立完成(chéng)複雜應用流程

√ 高效支持所有主流公鑰算法(RSA/ECC/SM2/SM9)

√ 支持最高4096位模運算

√ 支持橢圓曲線1024位運算(素域/二元域)

√ 支持Miller-Rabin素數測試算法

√ 支持加解密/簽名驗證/秘密推導

√ 支持秘鑰生成(chéng)(DSA/ECDSA/DH/ECDH等)

√ 對(duì)稱算法專用256位指令集

√ 哈弗體系結構

√ 支持絕大多數非公鑰算法:

☆ 分組密碼算法/流密碼算法/雜湊密碼算法

√ 可獨立運行,或與SEC緊耦合

√ 支持算法程序安全存儲

√ 256位随機數生成(chéng)

√ 内部随機數種(zhǒng)子生成(chéng)

√ 内部種(zhǒng)子可周期性自動更新

√ 可選的獨立專用随機數控制和訪問接口,易于其它模塊的直接調用

√ 1024個時鍾周期生成(chéng)256bits随機數,即每4個時鍾生成(chéng)1bit随機數

√ C*Core 32位超低功耗處理器